**RESEARCH ARTICLE**

OPEN ACCESS

# **Enhanced Skewed Load and Broadside Power Reduction in Transition Fault Testing**

# Mrs. A.Jyothi, Ms. P.Priyadharshika

1. Electronics and Communication Engineering, Arasu Engineering College, Kumbakonam, India

2. Electronics and Communication Engineering, Arasu Engineering College, Kumbakonam , India

## ABSTRACT

This Paper Proposes the T-algorithm technique to optimize the testing Skewed Load and Broadside architecture. And the architecture used to the compare the test pattern results. In this architecture, T-algorithm used to optimize the testing architecture. This architecture compare the test pattern output for the required any type of combinational architecture. The optimization process mainly focused by gate optimization for secure architecture. The proposed system to use the T-algorithm, to optimize the testing clocking level for the required test patterns. This technique to replace the flip flop and the mux arrangement. To reduce the flip flops in Skewed Load architecture. And to develop the accuracy for testing architecture. The proposed system consists of the secure testing architecture and includes the XOR-gate architecture. So the modification process applied by the Broadside and over all Skewed Load architecture. The proposed technique to check the scanning results for the testing process. The testing architecture mainly used to the error attack for the scanning process and the scanning process work with any type of testing architecture. The scanning process to be secure using the Talgorithm for the Skewed Load architecture. And to develop the testing process for the fault identification process. The diagnosis technique to detect error for the scanning process in any type combinational architecture. The T-algorithm used to reduce the circuit complexity for the testing architecture and the testing architecture used to reduce the delay level. And the future process, this technique used to reduce the gate level for the sticky comparator architecture and to modify the clocking function for the testing process. This technique to develop the accuracy level for the testing process compare to the present methodology.

**Keywords**: Broadside Transition, Reduction of Flip-flops, Reduction of circuit complexity, Skewed Load, XOR gate Architecture

## I. INTRODUCTION

The SOC's test application time is major problem in Industries. The efficient way of reducing test application time for core based SOC's is, by ordering the tests concurrently. Several cores are tested at a same time. This, way of testing increases switching activity in chip,this results in higher power consumption. There exist a tradeoff between power consumption and testing time. By scheduling the modules, increases test time cost but reduces power consumption. The power model used often is global Peak Power Model where single power value, highest of power curve is used to represent power curves of each test. The advantage of this scheduling algorithm in test pattern has to keep track single value per test.

Significant researches efforts have been expended in reduce power dissipation during launch and capture cycle at speed testing. At the expense of pattern count inflation, the peak power is reduced. A partitioning approach has been proposed in where power wise costly patterns are further analyzed via fault simulation to identify the location of care bits, which dictate the partitioning of the design during capture; with few problematic patterns such an approach can deliver power savings. Partitioning the design and testing one partition at a time has been proposed to reduce launch and capture power in BIST.

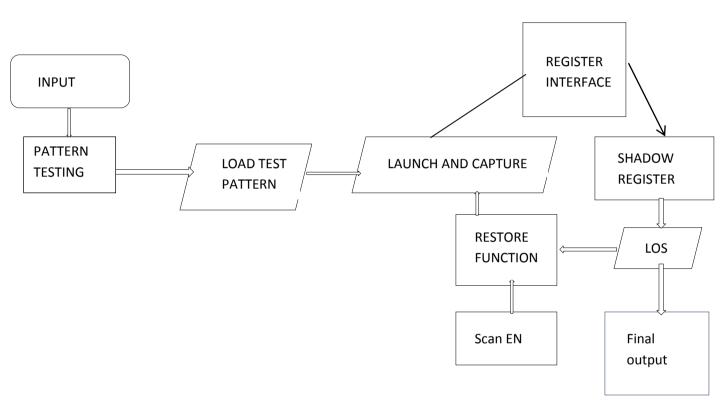

#### II. PROPOSED SYSTEM:

In skewed load and broadside transition, newly generated patterns aim for only one apportion at a time, this end up loading Interface registers of other partitions experiencing the penalty of test cost and data volume. Pattern count increases has been incurring even after the design is partitioned via ILP that minimizes capture violations. The proposed work is based on

T-algorithm based Enhanced Architecture. This algorithm optimizes scanning technology. This technique improves controllability of transition fault testing. Scan enable signal is not required to change at-speed. To identify the design regions, the s-graph is partitioned into strongly connected components. The SCC graph does not contain any cycles, delivers the acyclicity property of the graph. Acyclicity constraint still be met by merging operation of the cycle. Merging two operations of consecutive levels preserves the acyclicity of the graph; two regions from the same level can also be merged without introducing any cycles

To restore the Load state of interface register upon launch and capture operations, one shadow test register is inserted for each interface register. The shift register copies the content of

## **BLOCK DIAGRAM:**

Interface register, and during capture window, the shadow register is not clocked,, assuring the copied value in last shift cycle is retained. The newly inserted logic falls on test paths only, incurring to test penalty. The total cost for  $N_{int}$  interface registers is  $N_{int}$  muxes and  $N_{int}$ +2 flip-flops

#### LOAD STATE:

First the given input test pattern for the launch and capture operation. So we load the test pattern into the scan cell, the load state to be arrange the test inputs. A test pattern may launch transition from a set of flip-flops which may possibly span multiple regions and capture these transitions in the region being tested. The challenge is that any test pattern may be testing any set of regions by launching transitions from any other set of regions.

## LAUNCH OFF CAPTURE

The test pattern to apply the launch and capture process during the testing operation. To implement the launch off capture block into the load state. Region interface registers can be restored back to their load state upon launch and capture. DfT support that can restore the load state in interface registers in between the launch and capture operations in the design regions.

### **REGISTER BLOCKS**

There are two register used in this architecture. Upon every launch and capture operation that the interface registers gets involved in it. Its load state is restored by copying the content of the shadow register back into the interface register. Throughout the shift operations, the shadow register copies the content of the interface register. Effectively, a multiplexer and a shadow flip-flop are inserted for the interface register, doubling the size of the interface scan cell.

## LAUNCH OFF SHIFT

The test pattern to shift the next level using the Launch off Shift operation. As the LOS scheme launches transitions mainly followed by shift operation. The shadow registers can replace the bidirectional stitching for the restoration of the load state in LOS testing. A special stitching and the associated DfT support are required only for the interface registers in order to enable a proper rewind operation.

## **RESTORE FUNCTION**

To restore the load state of the interface register upon the launch and capture operations. DfT support for the load state restores mechanism. Effectively, a multiplexer and a shadow flip-flop are inserted for

the interface register, doubling the size of the interface scan cell. While the restore/rewind operations consume additional power. Our results show that this amount is always less than the power dissipated in the launch cycle, even after the launch power is reduced.

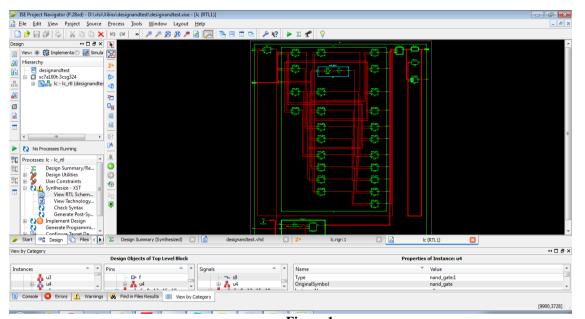

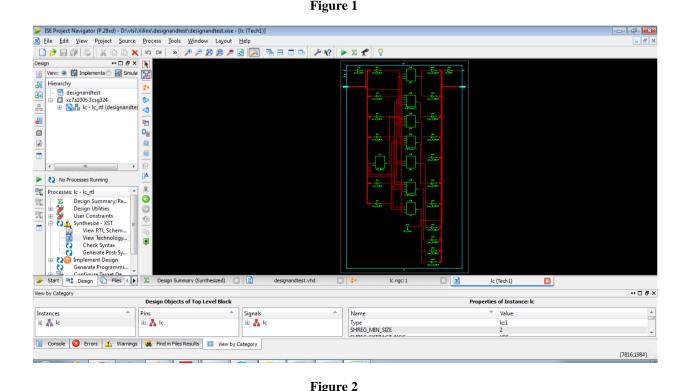

## SCHEMATIC DIAGRAM:

Figure 2

www.ijera.com

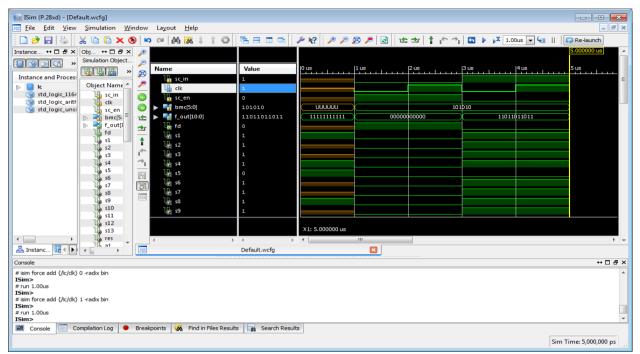

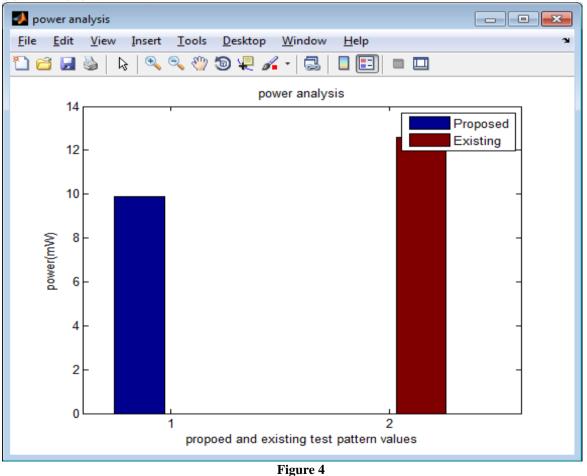

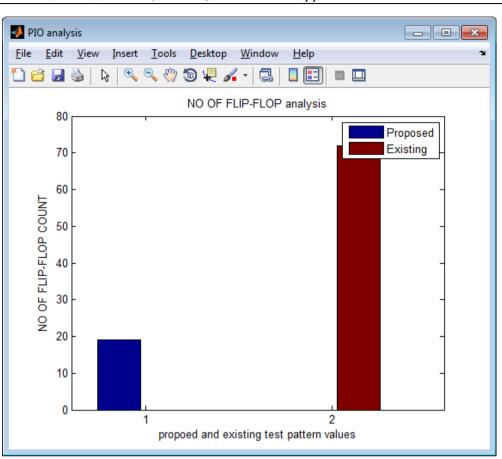

## **OUTPUT:**

Figure 3

## **COMPARISION TABLE:**

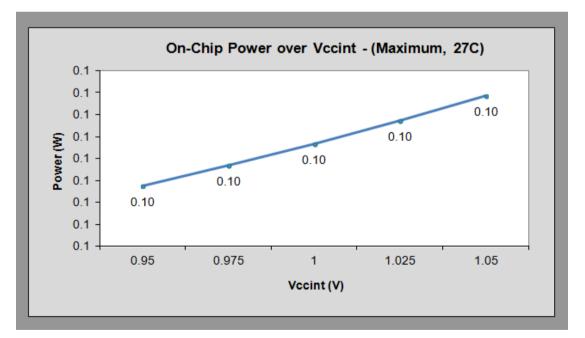

Figure 5

Figure 6

#### **III. CONCLUSION:**

The increasing test application times for testing modular core-based SoCs can be minimized by concurrent execution of the tests. However, concurrent test application leads to higher power consumption, which must be taken into account in order to not violate the power constraint. The power consumption has previously been modeled as a single value per test. The power model takes the scan chain switching activity generated by the test stimuli and the test responses into account. Further, the model provides a separate power profile per wrapper chain configuration. We have implemented the power model and included it in anSoCtest scheduling algorithm. We have made extensive experiments on several ITC'02 benchmarks and an industrial design, where we compare the testing time when using a single-value (global peak) power model and the proposed cycle-accurate power model.

We proposed DfT support that can restore the load state in interface registers in between the launch/capture operations in the design regions, enabling low-power LOC, LOS, and mixed at-speed testing. This way, a set of patterns optimized for cost and quality can be utilized as is, yet in a low power manner.

## **REFERENCES:**

- O. Sinanoglu, "Rewind-support for peak capture power reduction in launch-off-shift testing," in *Proc. 20th Asian Test Symp.*, Nov. 2011, pp. 78–83.

- [2] S. M. Saeed and O. Sinanoglu, "DfT support for launch and capture power reduction in launch-off-capture testing," in *Proc. 17th IEEE Eur. Test Symp.*, May 2012, pp. 1–6.

- [3] J. Savir and S. Patil, "On broad-side delay test," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 2, no. 3, pp. 368–372, Sep. 1994.

- [4] J. Savir and S. Patil, "Scan-based transition test," *IEEE Trans. Comput.Aided Design Integr. Circuits Syst.*, vol. 12, no. 8, pp. 1232–1241, Aug. 1993.

- [5] P. Girard, "Survey of low-power testing of VLSI circuits," *IEEE Design Test*, vol. 19, no. 3, pp. 82–92, May–Jun. 2002.

- [6] P. Girard, N. Nicolici, and X. Wen, Power-Aware Testing and Test Strategies for Low Power Devices. New York, USA: Springer-Verlag, 2010.

- [7] J. Saxena, K. M. Butler, V. B. Jayaram, S. Kundu, N. V. Arvind, P. Sreeprakash, and M. Hachinger, "A case study of IR-drop in structured at-speed testing," in *Proc. Int. Test Conf.*, Oct. 2003, pp. 1098–1104.

- [8] K. M. Butler, J. Saxena, T. Fryars, G. Hetherington, A. Jain, and J. Levis,

"Minimizing power consumption in scan testing: Pattern generation and DFT techniques," in *Proc. Int. Test Conf.*, Oct. 2004, pp. 355–364.

- [9] K. Agarwal, S. Vooka, S. Ravi, R. Parekhji, and A.S. Gill, "Power analysis and reduction techniques for transition fault testing," in *Proc. 17th Asian Test Symp.*, Nov. 2008, pp. 403–408.

- [10] K. Chakravadhanula, V. Chickermane, B. Keller, P. Gallagher, and P. Narang, "Capture power reduction using clock gating aware test generation," in *Proc. Int. Test Conf.*, Nov. 2009, pp. 1–9.

- [11] Z. Zhang, S. M. Reddy, I. Pomeranz, J. Rajski, and B. M. Al-Hashimi, "Enhancing delay fault coverage through low power segmented scan," in*Proc. 11th Eur. Test Symp.*, May 2006, pp. 21–28.

- [12] Z. Chen and D. Xiang, "Low-capture-power at-speed testing using partial launch-oncapture test scheme," in *Proc. 28th VLSI Test Symp.*, Apr. 2010, pp. 141–146.

- [13] Q. Xu, D. Hu, and D. Xiang, "Patterndirected circuit virtual partitioning for test power reduction," in *Proc. Int. Test Conf.*, 2007, pp. 1–10.

- [14] E. K. Moghaddam, J. Rajski, S. M. Reddy, and M. Kassab, "At-speed scan test with low switching activity," in *Proc. 28th VLSI Test Symp.*, 2010, pp. 177–182.

- [15] F. Wu, L. Dilillo, A. Bosio, P. Girard, S. Pravossoudovitch, A. Virazel, M. Tehranipoor, K. Miyase, X. Wen, and N. Ahmed, "Power reduction through X-filling of transition fault test vectors for LOS testing," in *Proc. 6th Int. Conf. Design Technol. Integr. Syst.*, Apr. 2011, pp. 1–6.

- [16] P. Girard, L. Guiller, C. Landrault, and S. Pravossoudovitch, "Circuit partitioning for low power BIST design with minimized peak power consumption," in *Proc. 18th Asian Test Symp.*, Nov. 1999, pp. 89–94.

- [17] H. F. Ko and N. Nicolici, "RTL scan design for skewed-load at-speed test under power constraints," in *Proc. Int. Conf. Comput. Design*, Oct. 2006, pp. 237–242.

- [18] H. F. Ko and N. Nicolici, "Automated scan chain division for reducing shift and capture power during broadside at-speed test," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 27, no. 11, pp. 2092–2097, Nov. 2008.

- [19] Z. Chen, K. Chakrabarty, and D. Xiang, "MVP: Capture-power reduction with minimum-violations partitioning for delay testing," in *Proc. IEEE ACM Int. Conf.*

Comput.-Aided Design, Nov. 2010, pp. 149–154.

- [20] V. R. Devanathan, C. P. Ravikumar, and V. Kamakoti, "Interactive presentation: On power-profiling and pattern generation for power safe scan tests," in *Proc. Design Autom. Test Eur. Conf.*, Apr. 2007, pp. 534– 539.

- [21] J. Lee, S. Narayan, M. Kapralos, and M. Tehranipoor, "Layout-aware, IR-drop tolerant transition fault pattern generation," in *Proc. Design Autom. Test Eur. Conf.*, 2008, pp. 1172–1177.

- [22] X. Wen, K. Miyase, S. Kajihara, H. Furukawa, Y. Yamato, A. Takashima, K. Noda, H. Ito, K. Hatayama, T. Aikyo, and K. K. Saluja, "A capturesafe test generation scheme for at-speed scan testing," in *Proc. 13th Eur. Test Symp.*, May 2008, pp. 55–60.

- [23] M.-F. Wu, H.-C.Pan, T.-H.Wang, J.-L.Huang, K.-H.Tsai, and W.-T. Cheng, "Improved weight assignment for logic switching activity during at-speed test pattern generation," in *Proc. 15th Asian South Pacific Design Autom. Conf.*, Jan. 2010, pp. 493–498.

- [24] P. M. Rosinger, B. M. Al-Hashimi, and N. Nicolici, "Scan architecture with mutually exclusive scan segment activation for shiftand capture power reduction," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 23, no. 7, pp. 1142–1153, Jul. 2004.

- [25] G. Karypis, R. Aggarwal, V. Kumar, and S. Shekhar, "Multilevel hypergraph partitioning: Applications in VLSI domain," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 7, no. 1, pp. 69–79, Mar. 1999.

- [26] R. Sankaralingam, N. A. Touba, and B. Pouya, "Reducing power dissipation during test using scan chain disable," in *Proc. 19th IEEE VLSI Test Symp.*, May 2001, pp. 319– 324.

- [27] K. Miyase, Y. Uchinodan, K. Enokimoto, Y. Yamato, X. Wen, S. Kajihara, F. Wu, L. Dilillo, A. Bosio, P. Girard, and A. Virazel, "Effective launch-to-capture power reduction for LOS scheme with adjacent probabilitybased X-Filling," in *Proc. 20th Asian Test Symp.*, Nov. 2011, pp. 90–95.